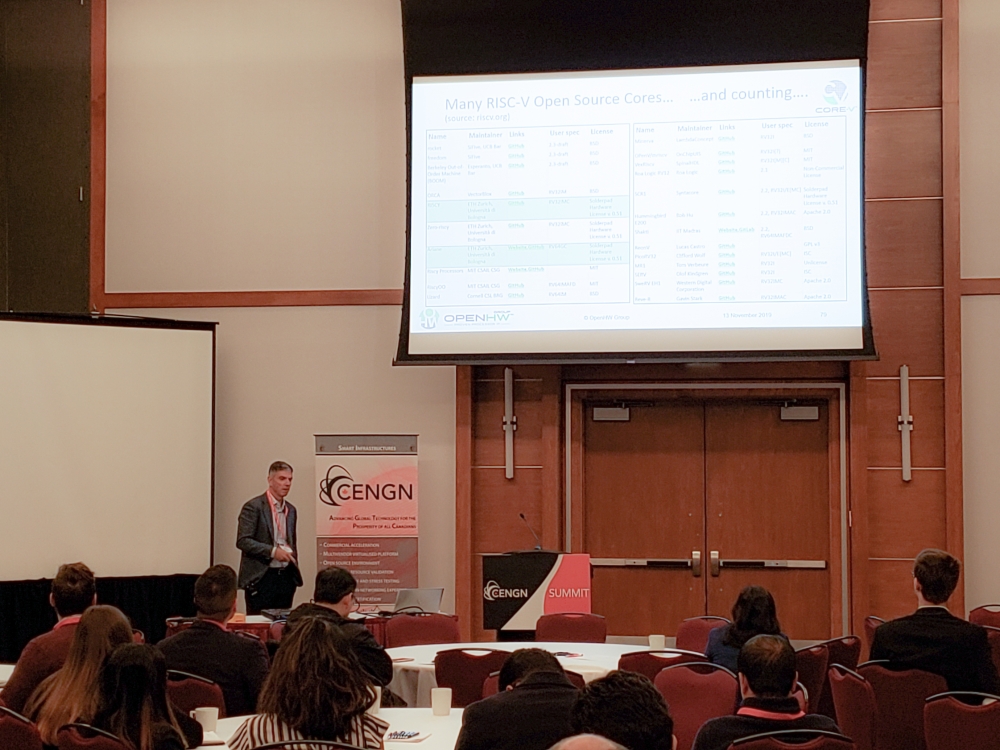

Open Source Processor IP for High Volume Production SoCs : CORE-V Family of RISC-V cores

This Technical Track session will describe barriers to adoption of open-source processor IP and opportunities to overcome these barriers.

This session will provide a brief overview of the RISC-V instruction set architecture and describe the CORE-V family of open-source cores that implement the RISC-V ISA. RISC-V (pronounced “risk-five”) is an open, free ISA enabling a new era of processor innovation through open standard collaboration. Born in academia and research, RISC-V ISA delivers a new level of free, extensible software and hardware freedom on architecture, paving the way for the next 50 years of computing design and innovation.

CORE-V is a series of RISC-V based open-source processor cores with associated processor subsystem IP, tools and software for electronic system designers. The CORE-V family provides quality core IP in line with industry best practices in both silicon and FPGA optimized implementations. These cores can be used to facilitate rapid design innovation and ensure effective manufacturability of production SoCs.

Technical Track Presentation: Open Source Processor Ip for high volume production socs: core-v family of risc-v cores

“The roll out of 5G and next generation networks requires new architectural approaches to realize ever increasing processing throughput within smaller and smaller power envelopes for devices connected at the edge and throughout the network. Open source hardware building blocks will be the next innovation frontier allowing the ecosystem to deliver these edge computing platforms.”

“The roll out of 5G and next generation networks requires new architectural approaches to realize ever increasing processing throughput within smaller and smaller power envelopes for devices connected at the edge and throughout the network. Open source hardware building blocks will be the next innovation frontier allowing the ecosystem to deliver these edge computing platforms.”

- Rick O'Connor